A. Luo, S. Bhattacharya, M. Miura-Mattausch, Y. Zhou and H. J. Mattausch, "Real-Time Surface Identification System for Variable Walking Speeds of Biped Robots," IEEE Embedded Systems Letters, doi: 10.1109/LES.2023.3299114.

S. Tayal, B. Majumdar, S. Bhattacharya and S. Kanungo, "Performance Analysis of the Dielectrically Modulated Junction-Less Nanotube Field Effect Transistor for Biomolecule Detection," IEEE Transactions on NanoBioscience, vol. 22, no. 1, pp. 174-181, Jan. 2023, doi: 10.1109/TNB.2022.3172702.

S. Tayal, Billel Smaani, Shiromani Balmukund Rahi, Sandip Bhattacharya, J. Ajayan "Incorporating Bottom-Up Approach Into Device/Circuit Co-Design for SRAM-Based Cache Memory Applications," IEEE Transactions on Electron Devices, vol. 69, no. 11, pp. 6127-6132, Nov. 2022, doi: 10.1109/TED.2022.3210070.

A. Luo, S. Bhattacharya, S. Dutta, Y. Ochi, M. M. Mattausch, J. Weng, Y. Zhou, and Hans Jürgen Mattausch, “Surface Recognition via Force-Sensory Walking-Pattern Classification for Biped Robot,” IEEE Sensor Journal, IEEE vol.21, no.8, pp.10061-10072, 2021 (SCI-3.076)

S. Bhattacharya, S. Dutta, A. Luo, M. M. Mattausch and H. J. Mattausch, “Energy Efficiency of Humanoid-Robot Walking on Indoor Surfaces with Different Walking Speeds”, IEEE Access, IEEE vol.8, pp. 227100-227112. 2020 (SCI-3.36)

S. Bhattacharya, A. Luo, S. Dutta, M. M. Mattausch and H. J. Mattausch, “Force-Sensor Based Surface Recognition with Surface-Property-Dependent Walking Speed Adjustment of Humanoid Robot”, IEEE Access, IEEE vol.8, pp.169640-169651. 2020 (SCI-3.36)

S. Bhattacharya, A. Luo, T. K Maiti, S. Dutta, M. M. Mattausch and H. J. Mattausch, “Surface-Property Recognition with Force Sensors for Stable Walking of Humanoid Robot”, IEEE Access, IEEE vol.7, no.1, pp. 146443-146456, 2019. (SCI-3.36)

S. Das, S. Bhattacharya, D. Das and H. Rahaman, “Modeling and Analysis of Electro-thermal Impact of Crosstalk Induced Gate Oxide Reliability in Pristine and Intercalation Doped MLGNR Interconnects", IEEE Transactions on Device and Materials Reliability, IEEE vol.19, no.3, pp.543-550, 2019. (SCI-1.58)

S. Bhattacharya, S. Das, A. Mukhopadhyay, D. Das and H. Rahaman, “Analysis of Temperature Dependent Delay Optimization Model for GNR Interconnect Using Wire Sizing Method", Journal of Computational Electronics, Springer-USA, vol.17, no.4, pp.1536-1548, 2018. (SCI-1.87)

S. Bhattacharya, D. Das and H. Rahaman, “Analysis of Simultaneous Switching Noise and IR-Drop in Side-Contact Multilayer Graphene Nanoribbon Power Distribution Network", Journal of Circuit, Systems & Computers, World Scientific Publisher, Singapore, vol.27, no.1, pp.1850001-17, 2018. (SCI-1.33)

S. Bhattacharya, D. Das and H. Rahaman, “Modeling and Performance Analysis of Graphene Nanoribbon Interconnects ", National Academy of Science Letter, Springer, vol. 40, no.5, pp.325-329, 2017. (SCI-0.78)

S. Bhattacharya, D. Das and H. Rahaman, “Analysis of Delay Fault in GNR Power Interconnects", International Journal of Numerical Modeling: Electronic Networks, Devices and Fields, Wiley, vol. 31, no.3, pp.1-16, 2017. (SCI-1.296)

S. Bhattacharya, D. Das, H. Rahaman “Reduced Thickness Interconnect Model using GNR to Avoid Crosstalk Effects”, Journal of Computational Electronics, Springer-USA, vol.15, no.2, pp.367-380, 2016. (SCI-1.87)

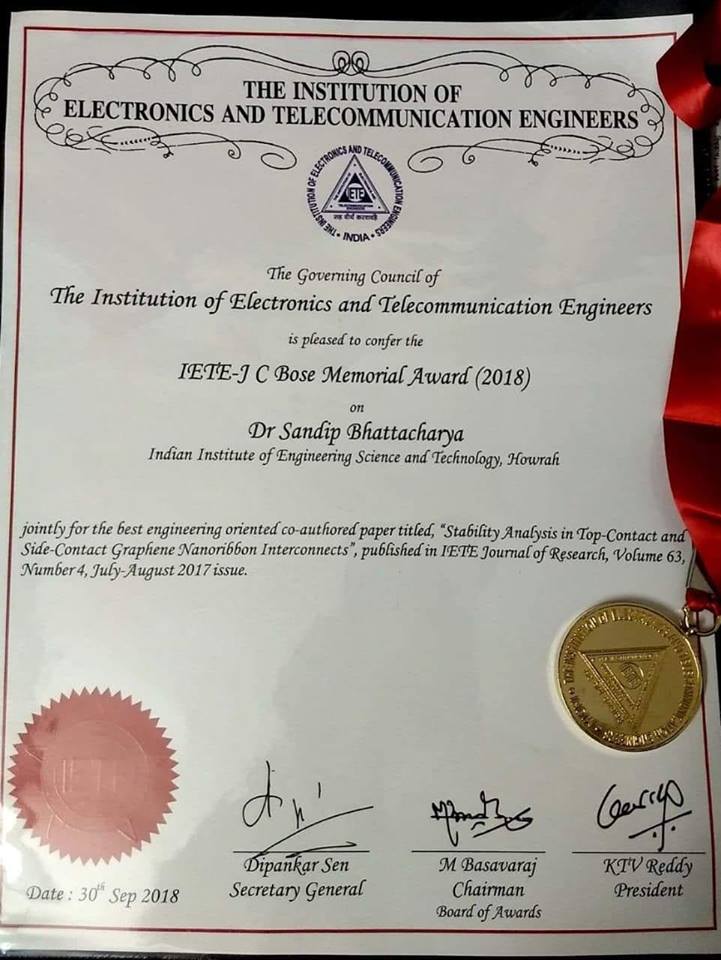

S. Bhattacharya, D. Das and H. Rahaman, “Stability Analysis in Top-Contact and Side-Contact Graphene Nanoribbon Interconnects", IETE Journal of Research, Taylor & Francis, vol.63, no.4, pp.588-596, 2017. (SCI-2.33)

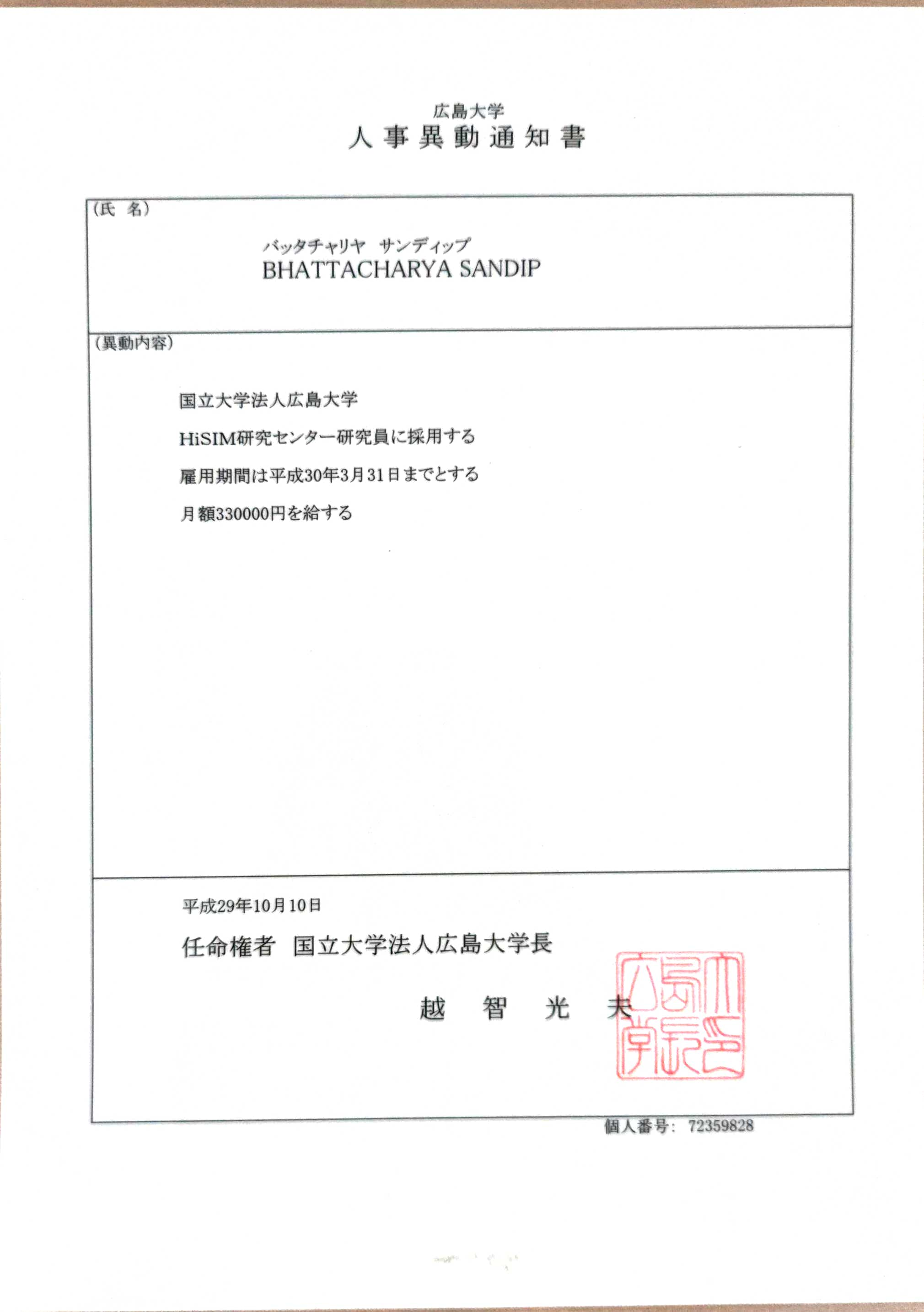

A. Mukhopadhyay, T.K. Maiti, S. Bhattacharya, T. Iizuka, H. Kikuchihara, D. Navarro, H. Rahaman, M. Miura-Mattausch, H. J. Mattausch, S. Yoshitomi, “Prevention of Highly Power-Efficient Circuits due to Short-Channel Effects in MOSFETs”, IEICE Transactions on Electronics, Japan, vol., no., pp., 2019. (SCI-0.6) [HiSIM and Toshiba Semiconductor]

S. Das, S. Bhattacharya, D. Das and H. Rahaman, “Thermal Stability Analysis of Graphene Nano Ribbon Interconnect and Applicability for Terahertz Frequency ", National Academy of Science Letter, Springer, vol., no., pp., 2019. (SCI-0.78)

S. Bhattacharya, D. Das and H. Rahaman, “Analysis of Temperature Dependent Power Supply Voltage Drop in Graphene Nanoribbon and Cu based Power Interconnects", AIMS Materials Science, AIMS Press-USA, vol.3, no.4, pp.1493-1506, 2016. (ESCI, Scopus).

S. Das, S. Bhattacharya, D. Das and H. Rahaman, “A Survey on Pristine and Intercalation Doped Graphene Nanoribbon Interconnect for Future VLSI Circuits", AIMS Materials Science, AIMS Press-USA, vol.8, no.2, pp.247-260, 2021. (ESCI, Scopus).

S Bhattacharya, M. I. Hussain, J Ajayan J, S Tayal, L.M.I Joseph, S Kollem, U Desai, S.M. Ahmed, and R. Janapati, Analysis of read speed latency in 6T-SRAM cell using multi-layered graphene nanoribbon and cu based nano-interconnects for high performance memory circuit design, ETRI Journal (2022), Wiley, 1–12.

Sandip Bhattacharya, Subhajit Das, Shubham Tayal, J. Ajayan, Leo Joseph, Tarun Kumar Juluru, Arnab Mukhopadhyay, Sayan Kanungo, Debaprasad Das, Shashank Rebelli, "Minimization of crosstalk noise and delay using reduced graphene nano ribbon (GNR) interconnect", Microelectronics Journal, Elsevier, Volume 127, 2022, 105533, ISSN 0026-2692, https://doi.org/10.1016/j.mejo.2022.105533.

S. Das, S. Bhattacharya, D. Das and H. Rahaman, "RF performance analysis of graphene nanoribbon interconnect," Proceedings of the 2014 IEEE Students' Technology Symposium, Kharagpur, India, 2014, pp. 105-110, doi: 10.1109/TechSym.2014.6807923.

S. Bhattacharya, S. Das, D. Das and H. Rahaman, "Electrical transport in graphene nanoribbon interconnect," 2014 2nd International Conference on Devices, Circuits and Systems (ICDCS), Coimbatore, India, 2014, pp. 1-4, doi: 10.1109/ICDCSyst.2014.6926148.

S. Bhattacharya, D. Das and H. Rahaman, "A Novel GNR Interconnect Model to Reduce Crosstalk Delay," 2014 Fifth International Symposium on Electronic System Design, Surathkal, India, 2014, pp. 5-9, doi: 10.1109/ISED.2014.9.

S. Bhattacharya, D. Das and H. Rahaman, "Temperature dependent IR-drop and delay analysis in side-contact multilayer graphene nanoribbon based power interconnects," 2016 20th International Symposium on VLSI Design and Test (VDAT), Guwahati, India, 2016, pp. 1-2, doi: 10.1109/ISVDAT.2016.8064891.

S. Bhattacharya, D. Das and H. Rahaman, "Delay minimization of multilayer graphene nanoribbon based interconnect using wire sizing method," 2016 International Conference on Microelectronics, Computing and Communications (MicroCom), Durgapur, India, 2016, pp. 1-6, doi: 10.1109/MicroCom.2016.7522500.

A. Mukhopadhyay et al., "MOSFET optimization toward power efficient circuit design," 2018 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, India, 2018, pp. 1-4, doi: 10.1109/ISDCS.2018.8379642.

S. Bhattacharya, S. Dutta, T. K. Maiti, M. Miura-Mattausch, D. Navarro and H. J. Mattausch, "Machine learning algorithm for autonomous control of walking robot," 2018 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, India, 2018, pp. 1-4, doi: 10.1109/ISDCS.2018.8379644.

S. Bhattacharya, A. Luo, T. K. Maiti, S. Dutta, M. Miura-Mattausch and H. J. Mattausch, "Fast Recognition and Control of Walking Mode for Humanoid Robot Based on Pressure Sensors and Nearest Neighbor Search," 2018 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS), Ishigaki, Japan, 2018, pp. 331-334, doi: 10.1109/ISPACS.2018.8923369.

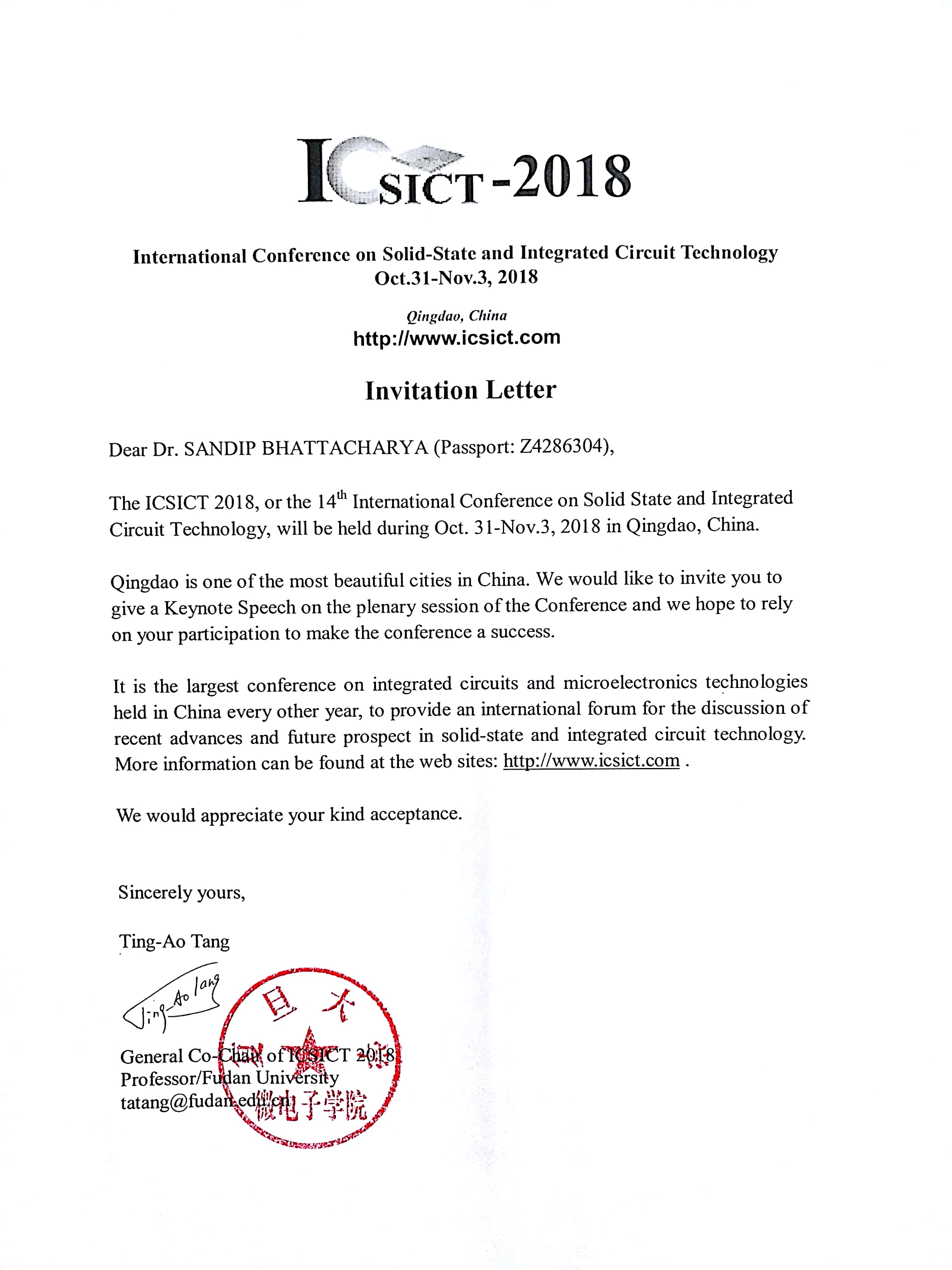

S. Bhattacharya, T. K. Maiti, S. Dutta, A. Luo, M. Miura-Mattausch and H. J. Mattausch, "System Simulation for Robot Control Based on AI Approach," 2018 14th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), Qingdao, China, 2018, pp. 1-4, doi: 10.1109/ICSICT.2018.8565654.

S. Dutta et al., "Self-controlled walking robot with gyro sensor network for stable movement on non-smooth surfaces," 2018 IEEE International Conference on Simulation, Modeling, and Programming for Autonomous Robots (SIMPAR), Brisbane, QLD, Australia, 2018, pp. 137-143, doi: 10.1109/SIMPAR.2018.8376283.

T. K. Maiti, S. Dutta, Y. Ochi, M. Miura-Mattausch, S. Bhattacharya and H. J. Mattausch, "Power Consumption Estimation of Biped Robot During Walking," 2019 2nd International Symposium on Devices, Circuits and Systems (ISDCS), Higashi-Hiroshima, Japan, 2019, pp. 1-4, doi: 10.1109/ISDCS.2019.8719095.

S. Das, S. Bhattacharya, D. Das and H. Rahaman, "Comparative Stability Analysis of Pristine and AsF5 Intercalation Doped Top Contact Graphene Nano Ribbon Interconnects," 2019 2nd International Symposium on Devices, Circuits and Systems (ISDCS), Higashi-Hiroshima, Japan, 2019, pp. 1-4, doi: 10.1109/ISDCS.2019.8719094.

S. Dutta et al., "Stability Analysis of Humanoid Robots with Gyro Sensors Subjected to External Push Forces," 2019 2nd International Symposium on Devices, Circuits and Systems (ISDCS), Higashi-Hiroshima, Japan, 2019, pp. 1-4, doi: 10.1109/ISDCS.2019.8719090.

A. Luo et al., "Dynamic Pattern-Recognition-Based Walking-Speed Adjustment for Stable Biped-Robot Movement under Changing Surface Conditions," 2019 IEEE 8th Global Conference on Consumer Electronics (GCCE), Osaka, Japan, 2019, pp. 600-601, doi: 10.1109/GCCE46687.2019.9015430.

H. J. Mattausch, A. Luo, S. Bhattacharya, S. Dutta, T. K. Maiti and M. Miura-Mattausch, "Force-Sensor-Based Walking-Environment Recognition of Biped Robots," 2020 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, India, 2020, pp. 1-4, doi: 10.1109/ISDCS49393.2020.9263005.

S. Das, S. Bhattacharya, D. Das and H. Rahaman, "A Short Review on Graphene Nanoribbon Interconnect," 2020 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, India, 2020, pp. 1-7, doi: 10.1109/ISDCS49393.2020.9263018.

Tiwari, A., Bahadursah, N., Bhattacharya, S., Kanungo, S. (2023). Analysis of the NH3 Adsorption on Boron-Arsenic Co-doped Monolayer Graphene: A First Principle Study. In: Giri, C., Iizuka, T., Rahaman, H., Bhattacharya, B.B. (eds) Emerging Electronic Devices, Circuits and Systems. Lecture Notes in Electrical Engineering, vol 1004. Springer, Singapore. https://doi.org/10.1007/978-981-99-0055-8_3

Tunga, S.G., Bhattacharya, S., Das, S., Rahaman, H. (2023). Modeling of Pristine and Intercalation Doped Multilayer Graphene Nanoribbon Conductors with Energy-per-Layer Screening. In: Giri, C., Iizuka, T., Rahaman, H., Bhattacharya, B.B. (eds) Emerging Electronic Devices, Circuits and Systems. Lecture Notes in Electrical Engineering, vol 1004. Springer, Singapore. https://doi.org/10.1007/978-981-99-0055-8_9

S. G. Tunga, S. Das, S. Bhattacharya and H. Rahaman, "Electrothermal modeling of Multilayer Graphene Nanoribbon (MLGNR) Interconnect considering Energy-per-Layer Screening," 2023 International Symposium on Devices, Circuits and Systems (ISDCS), Higashihiroshima, Japan, 2023, pp. 01-04, doi: 10.1109/ISDCS58735.2023.10153552.

Sandip Bhattacharya, Vijaya Baanala, Subhajit Das, Debaprasad Das, "Analysis of Power Supply Voltage Drop (IR-Drop) and Propagation Delay Using Folded Graphene Nano Ribbon Interconnect (F-GNR) Interconnect" Journal of Nano- and Electronic Physics; Sumy Ukraine Vol. 15, Iss. 1, (2023). DOI:10.21272/jnep.15(1).01017

S Bhattacharya, S Das, S Tayal, J Ajayan, L M I Leo Joseph; Analysis of Crosstalk Noise Using Graphene Nanoribbon Interconnects by Changing Wire Spacing and Electron Mean Free Path" Journal of Nano- and Electronic Physics; Sumy Ukraine Vol. 13, Iss. 6, (2021). DOI:10.21272/jnep.13(6).06031

S. Bhattacharya, A. Luo, S. Dutta, M. Miura-Mattausch and H. J. Mattausch, "Surface Recognition and Speed Adjustment of Humanoid Robot Using External Control Circuit," 2020 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, India, 2020, pp. 1-4, doi: 10.1109/ISDCS49393.2020.9263013.

Bhattacharya, S., Das, S., Tayal, S., Ajayan, J., Leo Joseph, L.M.I. (2023). AI-Enabled Circuit Design to Detect Walking Pattern for Humanoid Robot Using Force Sensor. In: Shukla, A., Murthy, B.K., Hasteer, N., Van Belle, JP. (eds) Computational Intelligence. Lecture Notes in Electrical Engineering, vol 968. Springer, Singapore. https://doi.org/10.1007/978-981-19-7346-8_30

_page-0001.jpg)